# **Digital Logic Design - Chapter 8-VHDL**

(In addition to the code include design documentation either as comments in the code or separate document.)

1S. Write a VHDL behavioral program to implement a pulse-triggered D latch.

#### Solution:

```

library IEEE;

use IEEE.std_logic_1164.all;

entity Vdlatch is

port (D, CLK: in std logic;

Q, QN: buffer std logic); -- note buffer is a new mode type.

end Vdlatch:

architecture Vdlatch b of Vdlatch is

begin

process (CLK, D)

begin

if (CLK = '1') then

Q \le D;

end if:

QN \le not Q:

end process:

end Vdlatch b;

```

1U. Write entity code for a (2-input) XNOR.

#### **Solution:**

2S. Complete a VHDL behavioral design for an edge-triggered D latch.

Note: The expression (**signal'event**) is only true when the signal is changing. This is referred to as the event attribute of the signal. This attribute in conjunction with process() should be considered in completing this design. <Why is "**signal'event**" even mentioned; the way that this is written suggests that **signal'event** was mentioned before.>

#### Solution:

"CLK'event is no required since the process will be entered only when CLK changes."

2U. Write a VHDL behavioral program to implement a rising-edge-triggered JK flip flop.

#### **Solution:**

3S. Design a VHDL model for a 16-bit register with Clock Enable, active-low Output Enable, and active-low Clear.

#### **Solution:**

```

library IEEE;

use IEEE.std logic 1164.all;

entity Vreg16 is

port (CLK, CLKEN, OE_L, CLR_L: in STD_LOGIC;

D: in STD LOGIC VECTOR (1 to 16);

-- Input bus

Q: out STD_ULOGIC_VECTOR (1 to 16));

-- output bus (three-

-- state, unresolved)

end Vreg16;

architecture Vreg16 of Vreg16 is

signal CLR, OE: STD LOGIC;

-- active-high version of

-- signals

-- internal Q signal

signal IQ: STD LOGIC VECTOR(1 to 16);

begin

process (CLK, CLR_L, CLR, OE_L, OE, IQ)

begin

CLR <= not CLR L;

OE <= not OE L;

if (CLR = '1') then

IQ \ll (others =>'0');

<Explain this line.>

elsif (CLK'event and CLK='1') then

if (CLKEN = '1') then

IQ \ll D;

end if;

end if:

if OE = '1' then

Q <= To_StdULogicVector(IQ);

<Explain this line.>

else Q \ll (others => 'Z');

<Explain this line.>

end if:

end process;

end Vreg16;

```

3U. Design a VHDL model for a 12-bit register with Clock Enable, active-high Output Enable, and active-high Clear.

#### Solution:

4S. Using VHDL, design a 4-to-1 MUX. The two bit input "sel", selects the input  $d_0$ - $d_3$  that is connected to output "f". For example when sel="01", f= $d_1$ .

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity MUX4 is

```

4U. Using VHDL, design a 8-to-1 MUX. The three bit input "sel", selects the input  $d_0$ - $d_8$  that is connected to output "f". For example when sel="010", f= $d_2$ .

### Solution:

5S. Design a 2-Bit Ripple Carry Adder with carry in and a carry out using VHDL.

```

Solution:

```

```

library ieee;

use ieee.all;

use ieee.std logic 1164.all;

use ieee.std_logic_unsigned.all;

entity adder2 b is

port ( ci : in std_logic;

--carry in signal

a, b: in std_logic_vector (1 downto 0);

--2 2-bit numbers, a and b

s: out std logic vector (1 downto 0);

--2-bit sum

co: out std_logic);

--carry out term or bit (overflow)

end adder2 b;

architecture dataflow of adder2 b is

signal sum: std_logic_vector (2 downto 0);

--Sets the signal 'sum' to a 3-bit number,

-- to account for an overflow bit (carry out)

begin

sum <= ('0' \& a) + b + ci;

--('0' & a) forces a to become a 3-bit number

s \le sum (1 downto 0);

-- in order to account for a carry-in bit

co \ll sum(2);

--sum(0) and sum (1) bits are the sum

-- of a and b

-- sum(2) is the carry-out bit (overflow)

end dataflow;

```

5U. Design a 8-Bit Ripple Carry Adder with carry in and a carry out using VHDL.

- 6S. Design the architectures for a rising edge D flip-flop for each of the following cases:

- a) with asynchronous reset using an if statement.

- b) with synchronous reset using an if statement.

- c) with synchronous reset using a wait until statement.

All of the architectures have the following entity declaration in common:

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity dff is

port (CLK,D,RESET: in std_logic;

Q: out std_logic);

end dff;

a) The asynchronous reset architecture using an if statement:

architecture asyn_reset of dff is

begin

process (CLK, RESET, D)

begin

if RESET = '1' then

Q \le '0';

elsif rising_edge (CLK) then

Q \leq D;

end if;

end process;

end asyn reset;

b) The synchronous reset architecture using an if statement:

architecture syn_reset of dff is

begin

process (CLK, RESET, D)

begin

if rising_edge (CLK) then

if RESET = '1' then

Q <= '0';

else

Q \leq D;

end if:

end if:

end process;

end syn_reset;

c) The synchronous reset architecture using a wait until statement:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity dff is

port (CLK,D,RESET: in std logic;

Q: out std_logic);

end dff;

architecture syn_reset of dff is

begin

```

process

-- no sensitivity list.

```

begin

wait until rising_edge (CLK);

if RESET = '1' then

Q <= '0';

else

Q <= D;

end if;

end process;

end syn reset;

```

- 6U. Design the architectures for a rising edge JK flip-flop for each of the following cases:

- a) with asynchronous reset using an if statement.

- b) with synchronous reset using an if statement.

- c) with synchronous reset using a wait until statement.

#### **Solution**

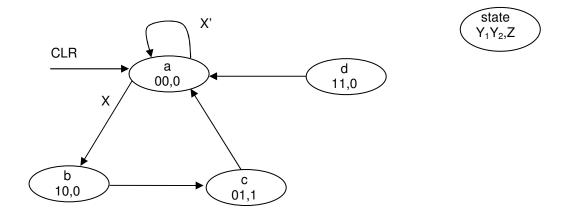

7S. Create a complete VHDL design for the system described by the following state diagram:.

```

library ieee;

use ieee.std_logic_1164.all;

entity fsm_1_d is

port (CLK, CLR, X: in std logic;

Y: out std logic vector (1 to 2);

Z: out std logic);

end fsm_1_d;

architecture design of fsm_1_d is

type state_type is (a, b, c, d);

signal PS, NS: state_type;

begin

sync proc: process (CLK, CLR, NS)

begin

if (CLR = '1') then

PS <= a:

Z \le '0';

elsif rising edge (CLK) then

```

```

PS <= NS;

end if:

end process sync_proc;

comb_proc: process (PS, X)

begin

case PS is

when a => Z <= '0';

if X = '1' then

NS \le b;

else

NS \le a;

end if;

when b => Z <= '0';

NS \leq c;

when c => Z <= '1';

NS \le a;

when others \Rightarrow Z <= '0';

NS \le a:

end case:

end process comb_proc;

with PS select

Y \le 00" when a,

"10" when b,

"01" when c,

"11" when d,

"00" when others;

end design;

```

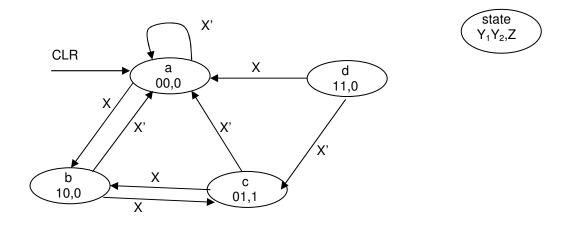

7U. Create a complete VHDL design for the system described by the following state diagram:.

### **Solution:**

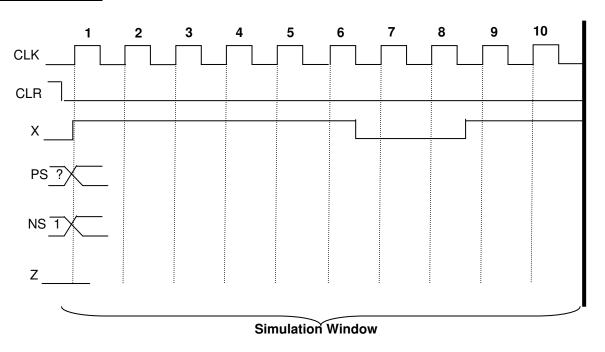

8S. Complete the timing diagram in simulation window drawn at the bottom of the page based on the following the VHDL Code segment:

library IEEE; use IEEE.STD\_LOGIC\_1164.all; entity quiz\_ent is

```

port (CLK, CLR, X: in std_logic;

Z: out std_logic

end quiz_ent;

architecture quiz_arch of quiz_ent is

Signal PS, NS: integer;

begin

proc_a: process (CLK, CLR)

begin

if (CLR = '1') then

NS \leq 1;

elsif rising_edge (CLK) then

PS <= NS;

If ( NS < 2^{**}8 and x='1') then NS <= NS^*2;

elsif (NS > 0 and x=0) then NS <= NS/2;

end if;

end process proc_a;

proc_b: process (PS, X)

begin

if (PS > 31) then Z <= '1';

else Z <= '0';

end if;

end process proc_b;

end quiz_arch;

```

### **TIMING DIAGRAM**

| Name         | Value | Stimulator |   | ı 10   | - 1 20 | 0 - 1 - 30 | ) 1 4,0 | 1 - 1 - 50  | · i 60 | - 1 - 7,0 | 80  | 9,0 | i i 10 | 0 1 1 <b>1</b> 0 |

|--------------|-------|------------|---|--------|--------|------------|---------|-------------|--------|-----------|-----|-----|--------|------------------|

| ► CLK        | 0     | Clock      |   | $\Box$ |        |            |         |             |        |           |     |     |        |                  |

| CLR          | 0     | Formula    |   |        |        |            |         |             |        |           |     |     |        |                  |

| <b>D-</b> X  | 1     | Formula    |   |        |        |            |         |             |        |           |     |     |        |                  |

| <b>™</b> PS  | 64    |            |   | X1     | X2     |            |         | <b>\(16</b> | (32    | 64        | (32 | X16 | (32    | (64              |

| <b>™</b> NS  | 128   |            | Œ | X2     | X4     | X8         | (16     | X32         | 64     | 32        | (16 | (32 | (64    | (128             |

| <b>-</b> • Z | 1     |            |   |        |        |            |         |             |        |           |     |     |        |                  |

|              |       |            |   |        |        |            |         |             |        |           |     |     |        |                  |

8U. Write VHDL code for a vending machine that accepts 5, 10 and 25 cents coins and deliver the product when \$1 has been deposited.